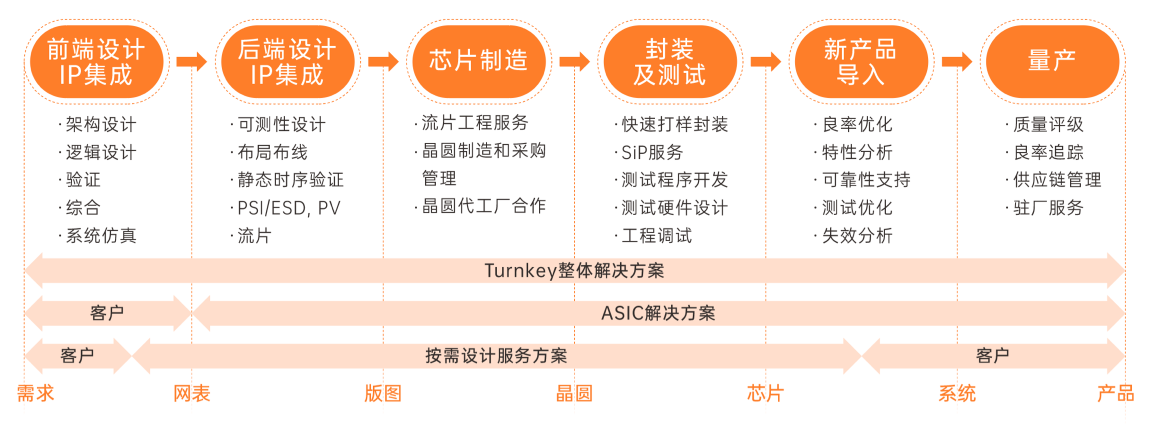

· Spec到芯片

· Netlist到芯片

· Spec到GDS

· Netlist到GDS

· 人力外包

· 数字前端+后端设计服务整包

· 后端设计服务整包

· 数字前端+后端设计服务turnkey

· 后端设计服务turnkey

· 低功耗设计

· 多电源域设计

· 混合信号设计

· 高速电路设计

· 射频电路设计

· 摩尔精英自有的专业设计服务流程(Moore Flow)和交付过程控制,支持业界主流工具,为客户的设计服务提供有力保证。

· 安全设计中心

· 设计团队经验丰富

· 设计流程可靠

· 高效客户沟通

打造设计服务平台,充分融合自有团队和合作伙伴团队的人员,提供1+1>2的服务

· 总计400+工程师,硕士及博士学历>40%,

· 丰富的工作经验, 58%工程师>5年经验, 涵盖不同类型的设计服务需求

· 高效及高质量的交付

| 芯片应用 | Process | |

| 物联网 | NBIoT | 40ULP |

| IoT | 55eflash | |

| SoC | 网络芯片 | 16nm |

| 网络芯片 | 14nm | |

| 导航 SoC | 55nm | |

| 通信模块 | 28nm | |

| 通信模块 | 16nm | |

| AP | 28nm | |

| AP | 16nm | |

⽬标应⽤:⽆线存储, 应⽤于SD卡+WIFI

制程:180nm eFlash (可移植)

合作模式:

a. 基于SoC设计框架原型

b. 提供底层驱动软件

c. 前后端芯⽚设计

d. FPGA原型开发

e. 供应链服务(流⽚、封装、测试)

f. ⼩规模定制服务

· Die size=~12sq. mm (180nm)

· 量产良率期望⼤于 98%

· 开发周期规划:从规格固化到回⽚测试约1年时间

⽬标应⽤:⽹络包处理芯⽚

制程:28nm

合作模式:ASIC

Critical path frequency: 800MHZ

Die size = 82 mm²

芯⽚整体趋向IO limited, 部分的block利⽤率⼤于70%

设计服务的前后端协同与反复迭代优化

主要IP信息:

· CPU: ARM cortex-M3

· DDR4 memory controller+PHY,64bits, 3200MHZ, x2

· PCIE Gen3 controller+PHY, 16 lanes

· 25G SerDes x4 lanes, x2

⽬标应⽤:导航芯⽚

制程:55nm

合作模式:产品委托设计与供应链管理 Die size= 25 mm²

项⽬特点:

· 芯⽚较⼤STA收敛挑战 复杂的数据流梳理

· 从产品规格到量产⼀体化的项⽬⽅案

· DFT需求

· 产品设计周期的挑战

⽬标达成:带有DFT的MPW设计⼀次性成功直接⽤于NTO量产流⽚。

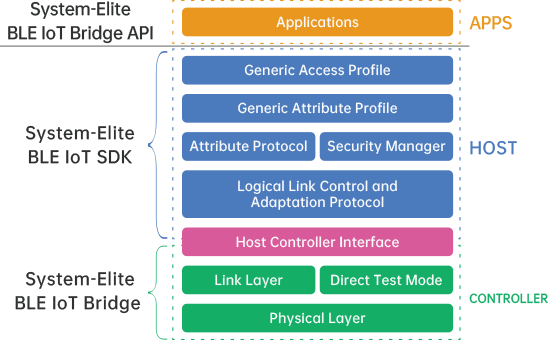

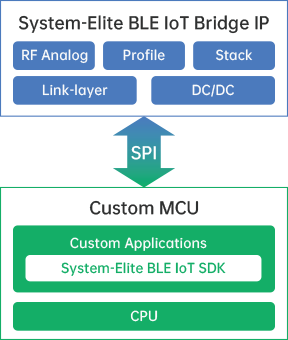

· 针对没有BLE基础的MCU程序员订制,最容易上手的BLE数据交换API

· 经认证的 BT 5.0 Bluetooth Low Energy 低功耗蓝牙 controller sub-system

· 出色的射频性能和抗干扰能力

· 集成 PMU 和 DC/DC

智能温度计、血压监测仪、血糖计

· 体重计

· 智能位置信标(Beacon)

· 智能标签

· 移动刷卡机(mPOS)

· 遥控玩具

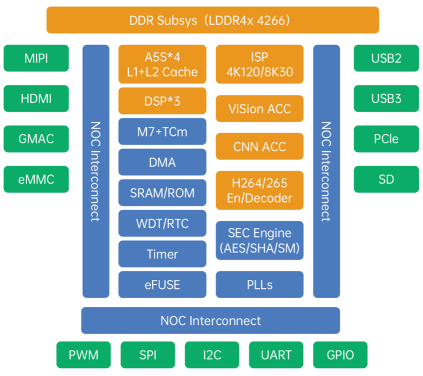

新⼀代AI芯⽚

· 商业模式:RTL to GDS

· 制程:16nm

· 基于设计挑战,客户期望与有经验的团队合作,针对极具挑战的DDR5设计,期待能够⼀版达到成功,同时希望团队在FINFET⼯艺下经验丰富,并由具备全局掌控能⼒的负责⼈带队,确保双⽅配合顺利。

· 客户对于项⽬数据安全极其重视,需要确保任何项⽬相关数据不能泄漏。